撰稿人:郑丽霞

单位:东南大学 集成电路学院

郑丽霞, 吴金, 孙伟锋, 万成功, 刘高龙, 王佳琦, 顾冰清. SPAD阵列读出电路关键技术与发展趋势(特邀)[J]. 红外与激光工程, 2023, 52(3): 20220903. doi: 10.3788/IRLA20220903

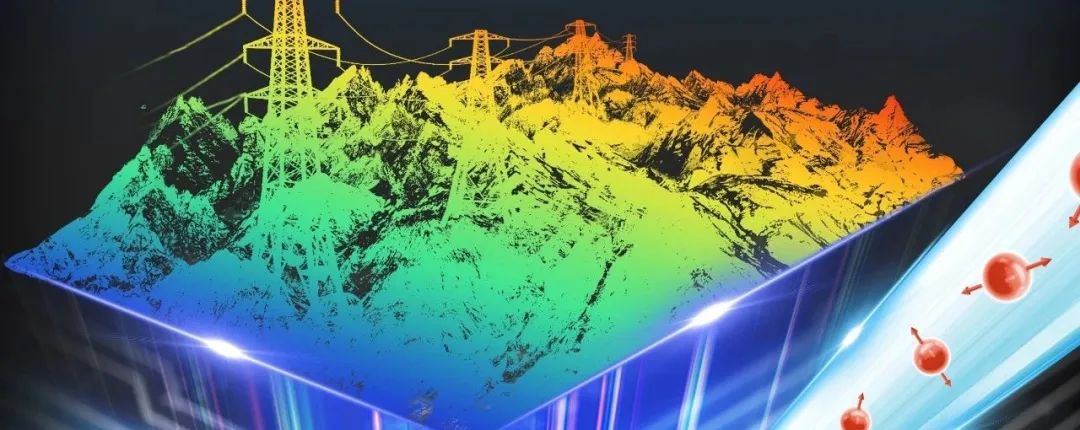

近年来,具有单光子检测能力的单光子雪崩二极管(Single Photon Avalanche Diode, SPAD)以其灵敏度高、响应速度快、抗干扰能力强、体积小等优点,在诸如激光雷达、量子通信、荧光光谱分析等弱光探测领域得到了广泛应用。SPAD的各类应用需要检测探测器信号的读出电路(Readout Integrated Circuit, ROIC)与之配套,以实现SPAD雪崩信号的快速提取与片上处理。SPAD各类应用对阵列规模、探测器信号的提取和处理能力的要求越来越高,而大规模阵列导致的寄生效应、功耗、面积等问题越来越突出,严重影响成像质量,阵列型SPAD读出电路的设计面临很大的挑战。而如果要与高性能SPAD阵列匹配,读出电路就必须具备高速、高精度、低功耗的性能特点。因此,单光子探测技术的发展既依赖于先进传感器的研制,又离不开具备雪崩信号检测与处理能力的专用集成电路的研发。

典型的基于光子飞行时间(Time of Flight, TOF)的成像系统架构如图1所示,系统工作时,首先由主机/延时器发出系统启动指令,ROIC完成测量前的电路复位,系统处于待测状态。随后主机发出激光发射指令EN,激光器向目标发射激光,同时ROIC中所有像素的时间-数字转换器(Time-to-digital Converter, TDC)开始计时。直到像素的探测器检测到目标反射的光子,TDC才停止计时。ROIC再将各个像素量化后的数据逐像素传出,实现图像处理与显示。作为成像系统中的核心单元,ROIC需要为SPAD提供最佳偏置工作条件,并提取雪崩信号,随后对雪崩信号进行高精度、高速实时处理和数据传输。其中,对探测器雪崩信号进行检测的电路被称为接口电路,接口电路为SPAD探测器提供不同探测状态的偏置电压,并完成雪崩信号的检测和雪崩淬灭,最后输出标准数字信号供后续电路处理。后续电路根据系统具体成像应用的需求,对雪崩信号执行数字量化、计算等操作,最终转换、输出为遵循一定格式要求的数据。按照对返回光子的处理方式,主要有光子计时、光子计数两类信号处理电路,分别对应主动/被动成像应用。

传统接口电路的基本功能是实现雪崩信号的提取与淬灭,输出标准数字信号供后级电路进行处理,近年来随着SPAD阵列规模的不断扩大,各研究团队对SPAD接口电路也有了更高的要求和更深入的研究。为了解决阵列型SPAD击穿电压不一致的问题,接口电路具备了区域级或像素级调节SPAD反向偏压的功能,可以分区域,甚至逐个像素精确调节反向偏压。东南大学提出了一种可用于阵列的反偏电压调节电路。如图2所示,SPAD增益波动抑制电路采用DAC方式提供偏置点电压,该电路位于像素外部,并与内部主动淬灭电路配合完成偏压调节与雪崩淬灭。工作原理如下:首先根据每个SPAD探测器的击穿电压,确定每个像素调节电压的数字码。将所有像素的数字码通过串行总线的方式输入电路,并通过移位寄存器传输给每个数据选择器进行电压选择,同时将电压调节器各结点输出电压提供给每个选择该电压的像素,进而实现多像素APD的反偏电压可调,通过调节之后,阵列的暗计数一致性得到明显改善。此外,SPAD阵列的公共电极电压均为10V以上,远远高于ROIC的电源电压,为了保护读出电路,需要在电路上加入高压击穿保护电路,但由于ROIC的工艺一般为普通CMOS工艺,耐压能力在5V以内,而高压管非常占用面积,无法在像素内集成,目前有一些研究团队提出了一些击穿保护电路结构,但在阵列应用中目前尚无较好的解决方案。

在基于光子飞行时间的应用中,由于光子到达时间不一致,理论上每个像素均需要独立的TDC进行TOF的测量。利用时间放大、时间追赶等电路架构,传统独立TDC的时间分辨率已经可以达到1ps以下。但是,由于像素电路受到严格的面积和功耗限制(一般要求像素中心间距在50μm以下),所以上述高精度TDC中常用的实现方法无法用于阵列TDC,导致阵列型TDC的精度难以提升。其次在转换位数有限的条件下,TDC的量化精度和量程相互制约。对于宽动态范围的量化场合,传统的单模式TDC难以协调精度和量程之间的矛盾。而且单模式TDC如需改善分辨率、提高精度,就需要不断减小量化单位,导致时钟频率不断提高、功耗显著增大,因此量化精度的提高也会受到系统功耗的限制。而由不同类型的单模式TDC共同组合(时空域变换)构成的分段式TDC,即有多种不同最低有效位作为量化单位的组合式TDC,能够以更低的代价高效实现多位量化,兼顾量程和精度,同时可以避免时钟频率和系统功耗的过度增加。瑞士洛桑理工学院是较早实现大面阵高精度读出电路的研究机构之一,该机构提出了一种基于TDC共享架构的低功耗ROIC,阵列规模扩展至128×128,时间分辨率最高可达97ps,系统架构如图3所示。在该阵列ROIC中仅有32个TDC模块,采用行扫描机制分时共享TDC,且一行中每四个像素为一组,一组共享一个TDC。由于采用TDC共享机制和逐行扫描方案,所以该系统仅需32个TDC即可实现128×128像素阵列的量化工作,极大地降低了系统功耗。又因为TDC位于像素阵列外部,不受像素面积的限制,所以可以采用一种较为复杂的多段式TDC架构,最终系统的时间分辨率能够达到百皮秒以内。

TDC共享方案通过减少系统中TDC的个数来实现低功耗,同时TDC面积不受单个像素单元的限制,因此可以采用多段式TDC、时间放大等方法提高时间分辨率。TDC共享方案可以兼顾功耗与精度,但牺牲了成像分辨率和检测效率。共享架构导致使用同一个TDC的像素每帧只能探测一个返回光子,因此TDC共享技术主要适用于成像实时性要求不高、光子稀疏的特定应用场合。

纵观国内外SPAD阵列读出电路的发展,其阵列规模的进展较为缓慢,除了制造工艺的问题外,读出电路的发展也遇到了技术瓶颈。主要的原因是随着阵列规模的增大,电路功耗成比例增加,尤其对于普遍需要制冷的SPAD探测器来说,此类问题影响更为严重,成为限制SPAD面阵规模进一步扩大的主要因素。事件驱动型TDC、像素共享型TDC的架构提出解决了一部分的功耗问题,但是随着ROIC时间分辨率精度的要求提升,电路工作频率的提高,以及电路功能的增加,功耗仍是一个较难解决的问题。其次SPAD探测器由于极高的增益,易产生暗计数,而暗计数引起的雪崩信号与光计数类似,电路难以区分,导致电路TOF的量化数据存在大量的无效数据,需要多帧检测进行数据融合,实际成像速度非常低。如何在电路硬件中融合去噪算法,也是今后读出电路需要重点解决的问题。随着SPAD阵列应用需求的进一步发展,读出电路将集成更多的功能,例如片上数据存储、返回光子事件多回波检测、自由探测模式等。SPAD阵列读出电路将进一步向感、存、算一体化方向发展,最终真正实现单芯片成像。

团队介绍:本研究团队隶属东南大学国家专用集成电路系统工程技术研究中心,是国内最早从事单光子探测读出电路研究的团队。课题组近十多年来一直与国内主要SPAD研制单位紧密合作,开展了InGaAs、HgCdTe 、SiC、Si材料SPAD读出电路的研究。SPAD读出电路相关授权发明专利20余项,拥有涉及ROIC电路系统架构、关键模块电路的完全自主知识产权,并实现了该类芯片的自主供货。先后完成了8X8、64X64、 256X64、256X128 SPAD阵列读出电路的研制,部分芯片目前已处于应用验证阶段,获得了良好的成像效果。

原文链接:

http://www.irla.cn/cn/article/doi/10.3788/IRLA20220903(阅读原文)转载/投稿/合作,请联系微信ivan_413598663

本文所用视频、图片、文字如涉及版权问题,请第一时间告知,我们将根据您提供的证明材料确认版权并按国家标准支付稿酬或立即删除。邮箱:liuxingwang@csoe.org.cn

文章转载自微信公众号:光电e+